Zacząłeś obserwować

Błąd związany z obserwowaniem użytkownika.

Ten użytkownik nie pozwala użytkownikom na obserwowanie go.

Już obserwujesz tego użytkownika.

Twój abonament pozwala na obserwowanie 0 projektów. Zmień poziom abonamentu na wyższy tutaj.

Udało się przestać obserwować

Błąd w zakończeniu obserwowania użytkownika.

Udało Ci się polecić

Błąd podczas polecania użytkownika

Coś poszło nie tak. Proszę odświeżyć stronę i spróbować ponownie.

Udało się zweryfikować adres e-mail.

singapore,

singapore

Obecnie jest 1:01 PM tutaj

Dołączył sierpnia 10, 2014

30

Zalecenia

Loi L.

@loi09dt1

6,9

6,9

84%

84%

singapore,

singapore

99%

Ukończone Projekty

93%

W Budżecie

97%

W czasie

14%

Powtórna Stawka Zatrudnienia

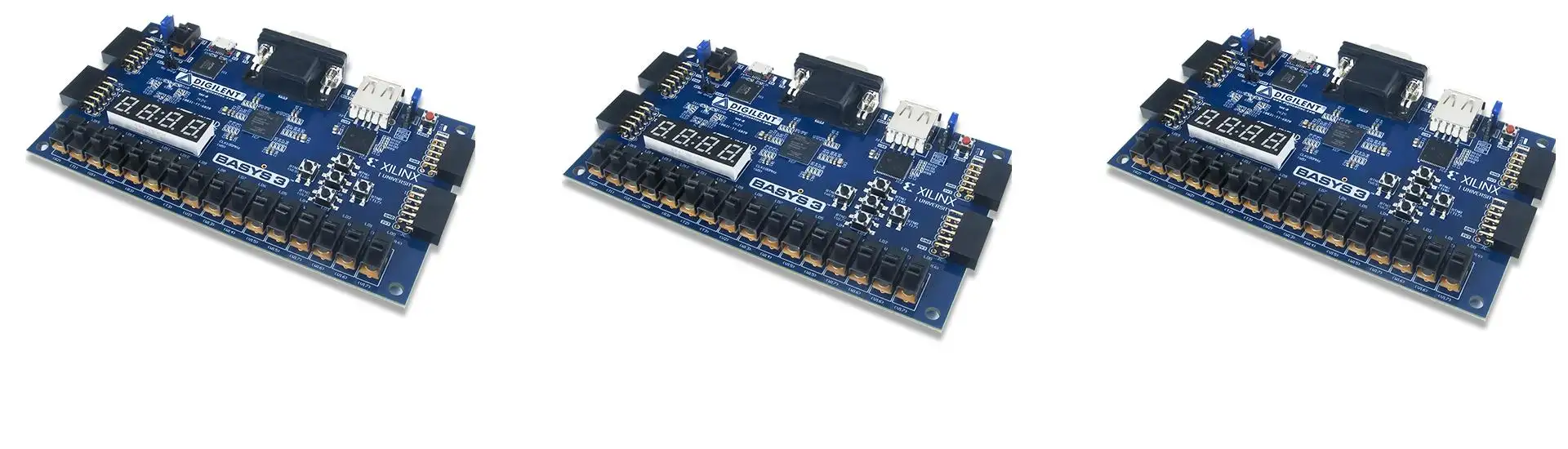

FPGA/Verilog/VHDL Expert

Skontaktuj się z Loi L. w sprawie projektu

Zaloguj się, aby omówić szczegóły na czacie.

Portfolio

Portfolio

Quadcopter Controller Board

Quadcopter Controller Board

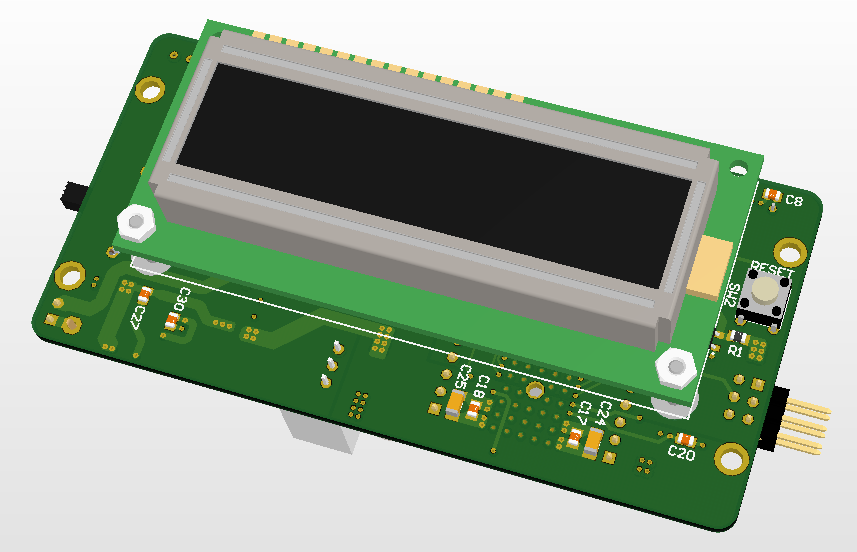

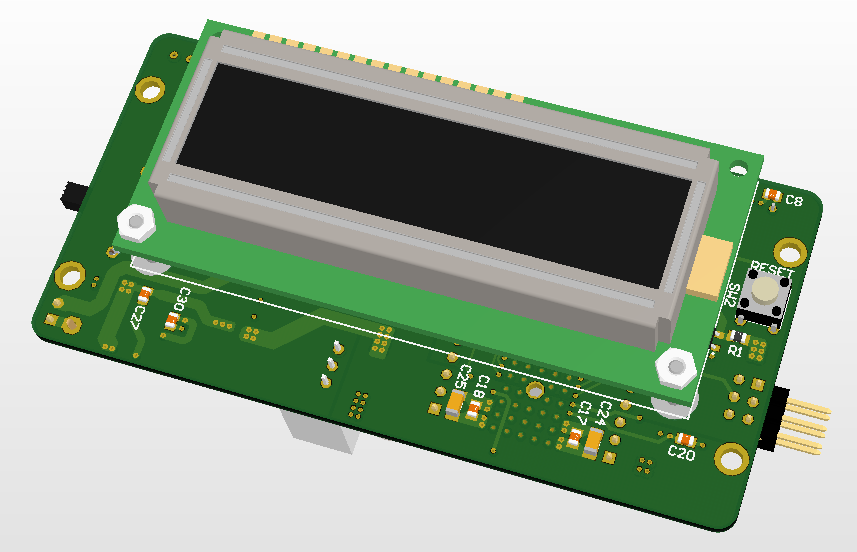

Magnet Controller using Android Apps - Shipped to US

Universal Remote + Camera + Wifi Module

Universal Remote + Camera + Wifi Module

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

4-Layers PCB Layout using Altium Designer

4-Layers PCB Layout using Altium Designer

RFID project

Quadcopter Controller Board

Quadcopter Controller Board

Magnet Controller using Android Apps - Shipped to US

Universal Remote + Camera + Wifi Module

Universal Remote + Camera + Wifi Module

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

4-Layers PCB Layout using Altium Designer

4-Layers PCB Layout using Altium Designer

RFID project

Oceny

Zmiany zapisane

Pokazuje 1 - 5 z 50+ komentarzy

$270,00 USD

C Programming

Engineering

Verilog / VHDL

Electrical Engineering

FPGA

A

•

$70,00 CAD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

•

$200,00 CAD

Electronics

Verilog / VHDL

Electrical Engineering

Arduino

FPGA

G

•

$150,00 USD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

+1 więcej

J

•

$80,00 USD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

+1 więcej

J

•

Doświadczenie

FPGA/Verilog/VHDL Developers

sty 2018 - Obecnie

Founder of FPGA4student. An experienced FPGA/Verilog/VHDL Engineer with more than 6 years experience and hundreds of FPGA projects in Verilog/ VHDL, Digital Logic/Circuit/System Design in LogiSim/CEDAR, and MIPS Assembly.

Expertise: Xilinx ISE, Vivado, Quartus, Modelsim, Logisim, CEDAR, Qtspim, MARS, PSpice, Altium, OrCAD, Proteus, Arduino.

Founder

lis 2016 - Obecnie

FPGA4student where shares free FPGA/Verilog/VHDL source code/ projects/ tutorials with EEE students.

Also offering FPGA/Verilog/VHDL Design/ Tutoring/ Consulting Services.

Experienced FPGA/Verilog/VHDL Engineer

sie 2014 - Obecnie

An experienced FPGA/Verilog/VHDL engineer with more than 6 years experiences on FPGA Design using Verilog/ VHDL, digital logic design LogiSim, Circuit design, MIPS Assembly, etc.

Edukacja

IC Design Course

(1 )

Bachelor of Engineering

(5 lat)

Kwalifikacje

IC Design Course Completion

Synopsys

2014

IC Design Course using Synopsys Design Tools

Odon Vallet scholarship

Prof. Odon Vallet and "Meeting Vietnam" Organization

2013

Scholarship for best performed students in central region of Vietnam in 2013

Intel Vietnam Engineering scholarship

Intel Vietnam

2012

Scholarship for top engineering students at DUT in 2011 and 2012

Publikacje

A FPGA-Based Embedded Fingerprint Identification System

the 2014 National Conference on Electronics, Communications and Information Technology – REV-ECIT 2014

A FPGA-Based Embedded Fingerprint Identification System on the 2014 National Conference on Electronics, Communications and Information Technology – REV-ECIT 2014

A FPGA-Based Embedded Fingerprint Identification System

The University of Danang

A FPGA-Based Embedded Fingerprint Identification System

Skontaktuj się z Loi L. w sprawie projektu

Zaloguj się, aby omówić szczegóły na czacie.

Weryfikacje

Certyfikaty

Najlepsze Umiejętności

Przeglądaj Podobnych Freelancerów

Przeglądaj Podobne Prezentacje

Zaproszenie wysłane pomyślnie!

Dziękujemy! Przesłaliśmy Ci e-mailem link do odebrania darmowego bonusu.

Coś poszło nie tak podczas wysyłania wiadomości e-mail. Proszę spróbować ponownie.

Wczytywanie podglądu

Udzielono pozwolenia na Geolokalizację.

Twoja sesja logowania wygasła i zostałeś wylogowany. Proszę, zalogować się ponownie.